泳道图简介

本文共 254 字,大约阅读时间需要 1 分钟。

1、简介

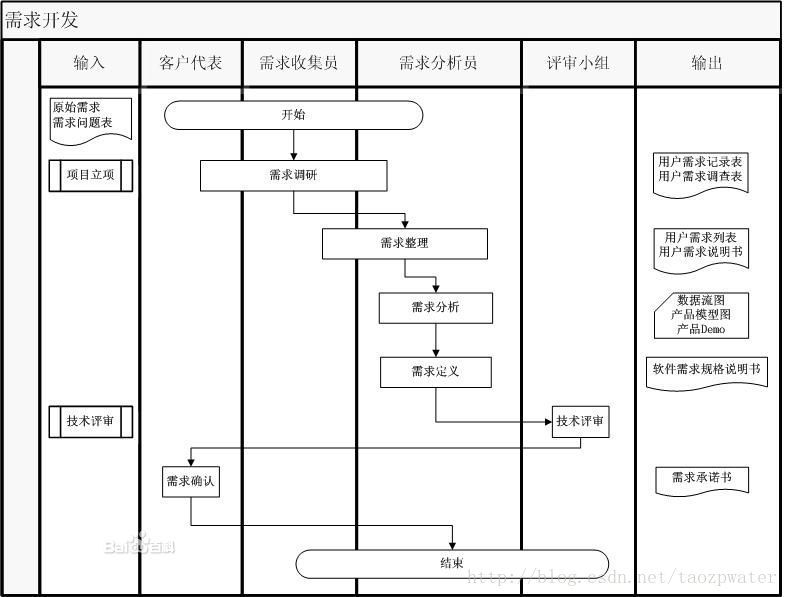

泳道图按角色划分为一个个泳道,每个角色的活动散落在各个角色对应的泳道里。泳道图是将模型中的活动按照职责组织起来。这种分配可以通过将活动组织成用线分开的不同区域来表示。由于它们的外观的缘故,这些区域被称作泳道。

2、绘制泳道展开图方法

⑴点出参与该流程的不同人员或工作功能,将他们列在海报或白板的左边或上方; ⑵透过脑力激荡列出流程中的步骤,并将其写在帖纸上; ⑶一一探讨这些步骤,并将贴纸贴在适当的泳道上; ⑷运用此结果来激发讨论应如何改善工作流程。

参考文献:百度百科和MBA lib

你可能感兴趣的文章

xilinx iMpact 923 warning信息的解决 (can not find cable,check cable setup!)

查看>>

iphone掉水里后的处理方法

查看>>

linux下nerdtree安装方法

查看>>

TCL中有关regexp匹配表达式的说明

查看>>

scandef格式详细说明

查看>>

gvim使用指南(学好就可下山了)

查看>>

Halide入门教程第2讲:处理图像

查看>>

Halide入门第3讲:如何设置环境变量以检查llvm编译生成的代码

查看>>

git 更新和冲突解决简单流程

查看>>

Lattice FPGA 使用指南1 - clarity designer出现ERROR – Error trying to create component 错误的解决办法

查看>>

verdi加载vhdl和verilog混合RTL设计的方法

查看>>

verdi编译vhdl文件时,报出"warning:*Warn* Unknown argument –vhdl08"的解决 办法

查看>>

linux 常见命令总结

查看>>

信号差分对的优势说明

查看>>

verilog timescale的两种仿真处理方法

查看>>

lattice FPGA 使用指南2 - DDR3 sdram controller IP配置注意事项

查看>>

何谓“pessimistic”异步FIFO的full和empty信号

查看>>

*Error* illegal LHS in continous assignment

查看>>

Cadence IUS 之一:简介

查看>>

在gvim中使用Emacs verilog mode的verilog代码自动插入和自动插入撤销的方法。

查看>>